# CA-IS2092 2.5kV<sub>RMS</sub> Isolated RS-485/RS-422 Transceivers with Integrated DC-DC Converter

#### 1. Features

- High-Performance and Compliant with RS-485

EIA/TIA-485 Standard

- 0.5Mbps data rate

- 1/8 unit load enables up to 256 nodes on the bus

- 3V to 5.5V supply voltage range, and the CA-IS2092VW provides individual logic supply input

- Integrated DC-DC Converter for Cable-side Power

- 3.3V and 5V output options ( $V_{ISO} \le V_{CC}$ )

- High integration with internal transformer

- Soft-start reduces input inrush current

- Overload and short-circuit protection

- Thermal shutdown

- Integrated Protection for Robust Communication

- 2.5kV<sub>RMS</sub> withstand isolation voltage for 60s (galvanic isolation)

- ±150kV/μs typical CMTI

- High lifetime: >40 years

- ±20kV Human Body Model(HBM) ESD protection on bus I/O, ±6kV HBM ESD protection on logic I/O

- True fail-safe guarantees known receiver output state

- Wide operating temperature range: -40°C to 125°C

- Wide-body SOIC16-WB(W) Package

- Safety Regulatory Approvals(pending)

- 3535V<sub>PK</sub> V<sub>IOTM</sub> and 849V<sub>PK</sub> V<sub>IORM</sub> per DIN VDE V0884-11:2017-01

- 2.5kV<sub>RMS</sub> isolation for 1 minute per UL 1577

- IEC 60950-1, IEC 60601-1 and EN 61010-1 certifications

- CQC, TUV, and CSA certifications

#### 2. Applications

- Industrial Automation Equipment

- Grid infrastructure

- Solar inverter

- Motor drivers

- HVAC

#### 3. General Description

The CA-IS2092x family of devices is galvanically-isolated RS-485/RS-422 transceivers with built-in isolated DC-DC converter, that eliminates the need for a separate isolated power supply in space constrained isolated designs. All devices of this family have the logic input and output buffers separated by a silicon oxide (SiO<sub>2</sub>) insulation barrier that provides up to  $2.5kV_{RMS}$  (60s) of galvanic isolation and  $\pm 150kV/\mu s$  typical CMTI. Isolation improves data communication by breaking ground loops and reduces noise where there are large differences in ground potential between ports. An integrated DC-DC converter generates the 3.3V or 5V operating voltage for the cable-side.

The CA-IS2092x family of devices is designed for multi-drop operation with high ESD protection of up to  $\pm 20$ kV HBM on the bus pins. The receiver is 1/8-unit load, allowing up to 256 transceivers (loads) on a common bus. These devices provide half-duplex transceivers, the driver and receiver enable pins let any node at any given moment be configured in either transmit or receive mode which decreases cable requirements. The individual logic supply input of CA-IS2092VW allows fully compatible 2.5V to 5.5V logic on logic input/output lines.

The CA-IS2092x series devices are available in wide-body 16-pin SOIC package which are the industry standard isolated RS-485/RS-422 package, and operate over -40°C to +125°C temperature range.

#### **Device Information**

| PART<br>NUMBER            | PACKAGE      | BODY SIZE (NOM)    |

|---------------------------|--------------|--------------------|

| CA-IS2092W<br>CA-IS2092VW | SOIC16-WB(W) | 10.30 mm × 7.50 mm |

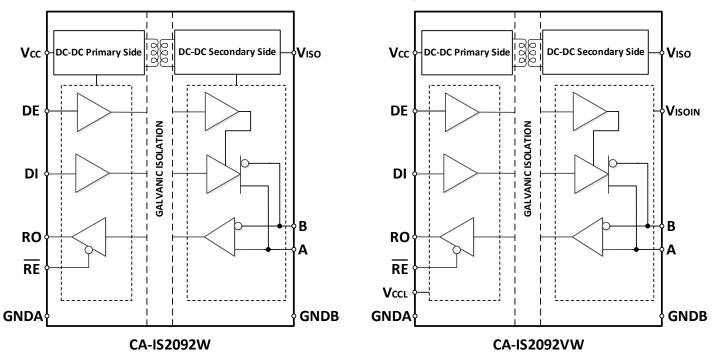

**CA-IS2092x Function Diagram**

#### 4. Ordering Information

| Table 4-1. Ordering Information |

|---------------------------------|

|---------------------------------|

| Part Number | Full/half duplex | Data Rate (Mbps) | V <sub>ISO</sub> (V) | V <sub>DDL</sub> | Package      |

|-------------|------------------|------------------|----------------------|------------------|--------------|

| CA-IS2092W  | Half-Duplex      | 0.5              | 3.3/5.0              | N/A              | SOIC16-WB(W) |

| CA-IS2092VW | Half-Duplex      | 0.5              | 3.3/5.0              | Yes              | SOIC16-WB(W) |

### Contents

| 1. | Featu | ures                                  | 1  |

|----|-------|---------------------------------------|----|

| 2. | Appli | ications                              | 1  |

| 3. | Gene  | eral Description                      | 1  |

| 4. | Orde  | ring Information                      | 2  |

| 5. | Revis | sion History                          | 3  |

| 6. | Pin C | Configuration and Description         | 4  |

| 7. |       | ifications                            |    |

|    | 7.1.  | Absolute Maximum Ratings <sup>1</sup> | 5  |

|    | 7.2.  | ESD Ratings                           | 5  |

|    | 7.3.  | Recommended Operating Conditions      | 5  |

|    | 7.4.  | Thermal Information                   | 5  |

|    | 7.5.  | Insulation Specifications             | 6  |

|    | 7.6.  | Safety-Related Certifications         | 6  |

|    | 7.7.  | Electrical Characteristics            | 7  |

|    | 7.7   | 7.1. Driver                           | 7  |

|    | 7.7   | 7.2. Receiver                         | 7  |

|    | 7.8.  | Supply Current                        | 8  |

|    | 7.9.  | Switching Characteristics             | 9  |

|    | 7.9   | 9.1. Driver                           | -  |

|    | 7.9   | 9.2. Receiver                         | -  |

|    | 7.10. | Typical Operating Characteristics     | 10 |

| 8.  | Param   | eter Measurement Information            | 14 |

|-----|---------|-----------------------------------------|----|

| 9.  | Detaile | ed Description                          | 17 |

|     | 9.1.    | Logic Input                             | 17 |

|     | 9.2.    | Fail-Safe Receiver                      | 17 |

|     | 9.3.    | Driver                                  | 18 |

|     | 9.4.    | Protection Functions                    | 18 |

|     | 9.4.    | 1. Signal Isolation and Power Isolation | 18 |

|     | 9.4.    | 2. Undervoltage Lockout                 | 18 |

|     | 9.4.    | 3. Thermal Shutdown                     | 19 |

|     | 9.4.    | 4. Current-Limit                        | 19 |

|     | 9.5.    | Isolated Supply Output                  | 19 |

| 10. | Applic  | ations Information                      | 20 |

|     | 10.1.   | Overview                                | 20 |

|     | 10.2.   | Typical Application                     | 21 |

|     | 10.3.   | 256 transceivers on the bus             | 21 |

|     | 10.4.   | PCB Layout                              | 22 |

| 11. | Packag  | ge Information                          | 23 |

| 12. | Solder  | ing Temperature (reflow) Profile        | 24 |

| 13. | Tape A  | nd Reel Information                     | 25 |

| 14. | Impor   | tant Statement                          | 26 |

#### 5. Revision History

| Revision Number | Description                                        | Page Changed |

|-----------------|----------------------------------------------------|--------------|

| Version 1.00    | Preliminary Version                                | N/A          |

| Version 1.01    | Changed t <sub>PHZ</sub> , t <sub>PLZ</sub> value. | 10           |

| Version 1.02    | Updated POD.                                       | 25           |

| Version 1.03    | Changed UL certification information.              | 7            |

6. Pin Configuration and Description

Figure 6-1. CA-IS2092W/CA-IS2092VW SOIC16 Top View

|                               | PIN N      | umber       | _            |                                                                                                                                                                                                                                                              |

|-------------------------------|------------|-------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name                          | CA-IS2092W | CA-IS2092VW | Туре         | Description                                                                                                                                                                                                                                                  |

| Vcc                           | 1          | 1           | Power Supply | Logic-Side Power Input and DC-DC converter supply input. Bypass $V_{CC}$ to GNDA with both 0.1µF and at least 10µF capacitors as close to the device as possible.                                                                                            |

| GNDA                          | 2, 8       | 2, 8        | GND          | Logic-Side Ground. GNDA is the ground reference for digital signals of logic side.                                                                                                                                                                           |

| RO                            | 3          | 3           | Digital I/O  | Receiver Data Output. Drive $\overline{\text{RE}}$ low to enable receiver $R_X$ . With $\overline{\text{RE}}$ low, RO is high when $(V_A - V_B) > -20$ mV and is low when $(V_A - V_B) < -200$ mV. RO is high impedance when $\overline{\text{RE}}$ is high. |

| RE                            | 4          | 4           | Digital I/O  | Receiver Output Enable. Driver $\overline{\text{RE}}$ low or connect to GNDA to enable R <sub>x</sub> .<br>Drive $\overline{\text{RE}}$ high to disable R <sub>x</sub> . RO is high-impedance when $\overline{\text{RE}}$ is high.                           |

| DE                            | 5          | 5           | Digital I/O  | Driver Output Enable. Drive DE high to enable bus driver outputs. Drive<br>DE low or connect to GNDA to disable bus driver outputs. DE has an<br>internal weak pull-down to GNDA.                                                                            |

| DI                            | 6          | 6           | Digital I/O  | Driver Input. With DE high, a logic low on DI forces the noninverting output (A) low and the inverting output (B) high; a logic high on DI forces the noninverting output high and the inverting output low.                                                 |

| V <sub>CCL</sub> <sup>1</sup> |            | 7           | Power Supply | Logic-supply input. $V_{CCL}$ is the logic supply voltage for logic-side input/output. Bypass to GNDA with a 1µF capacitor.                                                                                                                                  |

| NC                            | 7          |             |              | No internal connection on logic side.                                                                                                                                                                                                                        |

| GNDB                          | 9, 15      | 9, 15       | GND          | Cable Side Ground. GNDB is the ground reference for the RS-485/RS-422 bus signals.                                                                                                                                                                           |

| SEL <sup>2</sup>              | 10         | 10          | Digital I/O  | Output voltage $V_{ISO}$ select pin:<br>$V_{ISO}$ = 5.0 V when SEL is shorted to $V_{ISO}$ ;<br>$V_{ISO}$ = 3.3 V when SEL is shorted to GNDB or floating;                                                                                                   |

| NC                            | 11, 14     | 11          |              | No internal connection on cable side.                                                                                                                                                                                                                        |

| А                             | 12         | 12          | Bus I/O      | Non-inverting RS-485/RS-422 receiver input and driver output.                                                                                                                                                                                                |

| В                             | 13         | 13          | Bus I/O      | Inverting RS-485/RS-422 receiver input and driver output.                                                                                                                                                                                                    |

| V <sub>ISOIN</sub>            |            | 14          | Power Supply | Cable side power supply input. Bypass $V_{\text{ISOIN}}$ to GNDB with at least $1\mu\text{F}$ capacitor as close to the device as possible.                                                                                                                  |

| V <sub>ISO</sub>              | 16         | 16          | Power Supply | Isolated DC-DC power supply output. Cable Side Power supply. Bypass $V_{\rm ISO}$ to GNDB with both $0.1\mu F$ and at least $10\mu F$ capacitors as close to the device as possible.                                                                         |

#### Table 6-1. CA-IS2092W/CA-IS2092VW Pin Description and Functions

#### Notes:

1. Logic-Supply Input.  $V_{CCL}$  can be different voltage from  $V_{CC}$  supply, which allows fully compatible +2.7V to +5.5V logic for digital input/output.

V<sub>ISO</sub> ≤ V<sub>CC</sub>, this means if V<sub>CC</sub> = 3.3V, SEL pin must be floating or connected to GNDB and set the V<sub>IOS</sub> output to 3.3V; if V<sub>CC</sub> = 5.0V, there is no connection limit for SEL pin.

#### 7. Specifications

#### 7.1. Absolute Maximum Ratings<sup>1</sup>

|                                       | PARAMETER                                           | MIN  | MAX                         | UNIT |

|---------------------------------------|-----------------------------------------------------|------|-----------------------------|------|

| V <sub>CC</sub> , V <sub>CCL</sub>    | Logic-side Supply Voltage <sup>2</sup>              | -0.5 | 6.0                         | V    |

| V <sub>ISO</sub> , V <sub>ISOIN</sub> | Cable-side Supply Voltage <sup>2</sup>              | -0.5 | 6.0                         | V    |

| V <sub>IO1</sub>                      | Logic Voltage (DI, DE, $\overline{\text{RE}}$ , RO) | -0.5 | $V_{CC}/V_{CCL} + 0.5^{3}$  | V    |

| V <sub>IO2</sub>                      | Cable-side logic voltage (SEL)                      | -0.5 | $V_{ISO}/V_{ISOIN} + 0.5^3$ | V    |

| V <sub>BUS</sub>                      | Voltage on bus I/Os (A, B)                          | -8   | 13                          | V    |

| lo                                    | Output current on RO                                | -20  | 20                          | mA   |

| Tj                                    | Junction Temperature                                |      | 150                         | °C   |

| T <sub>STG</sub>                      | Storage Temperature                                 | -65  | 150                         | °C   |

| Notes:                                |                                                     | ·    |                             |      |

1. The stresses listed under "Absolute Maximum Ratings" are stress ratings only, not for functional operation condition. Exposure to absolute maximum rating conditions for extended periods may cause permanent damage to the device.

2. All voltage values except differential I/O bus voltages are with respect to the local ground (GNDA or GNDB) and are peak voltage values.

3. Maximum voltage must not be exceed 6V.

#### 7.2. ESD Ratings

|                                             | PARAMETER                                                                           |                                  | VALUE | UNIT |

|---------------------------------------------|-------------------------------------------------------------------------------------|----------------------------------|-------|------|

|                                             |                                                                                     | Bus pins to GNDB                 | ±20   |      |

| V <sub>ESD</sub> Electrostatic<br>discharge | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>1</sup> Other pins on cable | Other pins on cable-side to GNDB | ±6    | 1.17 |

|                                             |                                                                                     | All pins on logic-side to GNDA   | ±6    | kV   |

|                                             | Charged device model (CDM), per JEDEC specification JESD22-0                        | C101, all pins <sup>2</sup>      | ±2    |      |

| Notes:                                      |                                                                                     |                                  |       |      |

| 1. Per JEDEC docu                           | ument JEP155, 500V HBM allows safe manufacturing of standard                        | ESD control process.             |       |      |

| 2. Per JEDEC docu                           | ument JEP157, 250V CDM allows safe manufacturing of standard                        | ESD control process.             |       |      |

#### 7.3. Recommended Operating Conditions

|                  | PARAMETER                                             | Min                                     | Тур.     | Max                                     | Unit |

|------------------|-------------------------------------------------------|-----------------------------------------|----------|-----------------------------------------|------|

| Vcc <sup>1</sup> | Supply voltage on logic side                          | 3.15                                    | 3.3 or 5 | 5.5                                     | V    |

| V <sub>CCL</sub> | Logic supply voltage                                  | 2.375                                   | 3.3 or 5 | 5.5                                     | V    |

| Voc              | Common mode voltage at bus pins: A, B, Y and Z        | -7                                      |          | 12                                      | V    |

| V <sub>ID</sub>  | Differential input voltage V <sub>AB</sub>            | -12                                     |          | 12                                      | V    |

| RL               | Differential load                                     | 54                                      |          |                                         | Ω    |

| VIH              | Input high voltage (DI, DE to GNDA)                   | 2.0                                     |          | V <sub>CC</sub> /V <sub>CCL</sub> +0.3  | V    |

| VIL              | Input low voltage (DI, DE to GNDA)                    | -0.3                                    |          | 0.8                                     | V    |

| V <sub>IH</sub>  | Input high voltage (RE to GNDA)                       | 0.7 x V <sub>CC</sub> /V <sub>CCL</sub> |          | V <sub>CC</sub> /V <sub>CCL</sub> +0.3  | V    |

| V <sub>IL</sub>  | Input low voltage ( $\overline{\mathrm{RE}}$ to GNDA) | -0.3                                    |          | 0.3 x V <sub>CC</sub> /V <sub>CCL</sub> | V    |

| DR               | Data rate of the CA-IS2092W/CA-IS2092VW               |                                         |          | 0.5                                     | Mbps |

| T <sub>A</sub>   | Ambient Temperature                                   | -40                                     |          | 125                                     | °C   |

| Note:            |                                                       | •                                       |          |                                         |      |

#### 7.4. Thermal Information

|                  | THERMAL METRIC                         | CA-IS2092x   | 11   |

|------------------|----------------------------------------|--------------|------|

|                  |                                        | SOIC16-WB(W) | Unit |

| R <sub>0JA</sub> | Junction-to-ambient thermal resistance | 68.5         | °C/W |

#### CA-IS2092W, CA-IS2092VW

Version 1.03, 2023/05/23

#### Shanghai Chipanalog Microelectronics Co., Ltd.

CHIPANA

.0G

## 7.5. Insulation Specifications

|                                                         | PARAMETER                                                                              | TEST CONDITIONS                                                          | VALUE<br>W/T | וואט            |

|---------------------------------------------------------|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------|--------------|-----------------|

| CLR                                                     | External clearance                                                                     | Shortest terminal-to-terminal distance through air                       | 8            | mm              |

| CPG                                                     | PG External creepage Shortest terminal-to-terminal distance across the package surface |                                                                          | 8            | mm              |

| DTI                                                     | Distance through the insulation                                                        | Minimum internal gap (internal clearance)                                | 28           | μm              |

| CTI                                                     | Comparative tracking index                                                             | DIN EN 60112 (VDE 0303-11); IEC 60112                                    | >400         | V               |

|                                                         | Material group                                                                         | According to IEC 60664-1                                                 | II           |                 |

|                                                         |                                                                                        | Rated mains voltage ≤ 300 V <sub>RMS</sub>                               | I-IV         |                 |

| Overvolta                                               | Overvoltage category per IEC 60664-1                                                   | Rated mains voltage ≤ 400 V <sub>RMS</sub>                               | I-IV         |                 |

|                                                         |                                                                                        | Rated mains voltage ≤ 600 V <sub>RMS</sub>                               | -            |                 |

| DIN V V                                                 | /DE V 0884-11:2017-01 <sup>1</sup>                                                     |                                                                          | -            |                 |

| VIORM                                                   | Maximum repetitive peak isolation voltage                                              | AC voltage (bipolar)                                                     | 849          | V <sub>PK</sub> |

|                                                         |                                                                                        | AC voltage; time-dependent dielectric breakdown (TDDB) test              | 600          | VRM             |

| V <sub>IOWM</sub>                                       | Maximum operating isolation voltage                                                    | DC voltage                                                               | 849          | VDC             |

|                                                         |                                                                                        | V <sub>TEST</sub> = V <sub>IOTM</sub> , t=60 s (qualification);          | 2525         | V <sub>PK</sub> |

| V <sub>IOTM</sub>                                       | Maximum transient isolation voltage                                                    | V <sub>TEST</sub> = 1.2 × V <sub>IOTM</sub> , t=1 s (100% product test)  | 3535         |                 |

| V <sub>IOSM</sub> N                                     | Maximum surge isolation voltage <sup>2</sup>                                           | Test method per IEC 60065, 1.2/50µs waveform,                            | 4000         | V               |

|                                                         |                                                                                        | $V_{\text{TEST}} = 1.6 \times V_{\text{IOSM}}$ (production test)         |              | V <sub>PK</sub> |

|                                                         |                                                                                        | Method a, after input/output safety tests subgroup 2/3,                  |              | -               |

|                                                         |                                                                                        | $V_{ini} = V_{IOTM}, t_{ini} = 60s;$                                     | ≤5           |                 |

|                                                         |                                                                                        | $V_{pd(m)} = 1.2 \times V_{IORM}, t_m = 10s$                             |              |                 |

|                                                         |                                                                                        | Method a, after environmental tests subgroup 1,                          |              |                 |

| ~                                                       | Apparent charges                                                                       | V <sub>ini</sub> = V <sub>IOTM</sub> , t <sub>ini</sub> = 60s;           | ≤5           | ~               |

| <b>q</b> <sub>pd</sub>                                  | Apparent charge <sup>3</sup>                                                           | $V_{pd(m)} = 1.6 \times V_{IORM}, t_m = 10s$                             |              | pC              |

|                                                         |                                                                                        | Method b1, at routine test (100% production test) and                    |              |                 |

|                                                         |                                                                                        | preconditioning (sample test)                                            | ≤5           |                 |

|                                                         |                                                                                        | $V_{ini} = 1.2 \times V_{IOTM}$ , $t_{ini} = 1s$ ;                       | 20           |                 |

|                                                         |                                                                                        | $V_{pd(m)} = 1.875 \times V_{IORM}, t_m = 1s$                            |              |                 |

| CIO                                                     | Barrier capacitance, input to output <sup>4</sup>                                      | $V_{IO} = 0.4 \times sin (2\pi ft), f = 1 MHz$                           | ~0.5         | pF              |

|                                                         |                                                                                        | V <sub>IO</sub> = 500V, T <sub>A</sub> = 25°C                            | >1012        |                 |

| R <sub>IO</sub>                                         | Isolation resistance , input to output <sup>4</sup>                                    | $V_{IO} = 500V, 100^{\circ}C \le T_A \le 125^{\circ}C$                   | >1011        | Ω               |

|                                                         |                                                                                        | V <sub>IO</sub> = 500V at T <sub>S</sub> = 150°C                         | >109         |                 |

|                                                         | Pollution degree                                                                       |                                                                          | 2            |                 |

| UL 1577                                                 | 7                                                                                      |                                                                          |              |                 |

| V <sub>ISO</sub> Maximum withstanding isolation voltage |                                                                                        | $V_{\text{TEST}} = V_{\text{ISO}}$ , t = 60s (qualification),            | 2500         | V <sub>RM</sub> |

| V <sub>ISO</sub>                                        |                                                                                        | $V_{\text{TEST}} = 1.2 \times V_{\text{ISO}}$ , t = 1s (100% production) |              |                 |

2. Devices are immersed in oil during surge characterization.

3. The characterization charge is discharging charge (pd) caused by partial discharge.

4. Capacitance and resistance are measured with all pins on field-side and logic-side tied together.

#### 7.6. Safety-Related Certifications

| VDE(Pending)                             | UL                             | TUV(Pending)                           |

|------------------------------------------|--------------------------------|----------------------------------------|

| Certified according to DIN V VDE V 0884- | Certified according to UL 1577 | Certified according to EN 61010-1:2010 |

| 11:2017-01                               | Component Recognition Program  | (3rd Ed) and EN 60950-                 |

|                                          |                                | 1:2006/A2:2013                         |

| Certification number:                    | Certification number: E511334- | Certification number:                  |

| pending                                  | 20210507                       | pending                                |

#### 7.7. Electrical Characteristics

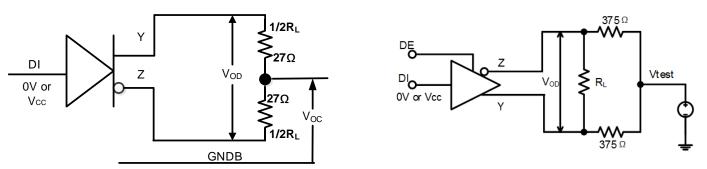

#### 7.7.1. Driver

All typical specs are at  $V_{CC} = 5V$ ,  $V_{CCL} = V_{CC}$ ,  $V_{ISOIN} = V_{ISO}$ ,  $T_A = 25$ °C, Min/Max specs are over recommended operating conditions unless otherwise specified.

|                                                | Parameter                                                               | Test Condition                                               | Min  | Тур.                | Max | Unit  |

|------------------------------------------------|-------------------------------------------------------------------------|--------------------------------------------------------------|------|---------------------|-----|-------|

|                                                | Driver differential output voltage                                      | $I_0$ = 0mA, unloaded bus. SEL = LOW or float                |      | 2.9                 |     | v     |

| V <sub>OD1</sub>                               | Driver differential output voltage                                      | $I_0$ = 0mA, unloaded bus. SEL = HIGH                        | 3.7  | 4.6                 |     | v     |

|                                                | Driver differential output voltage                                      | $R_L$ =54 $\Omega$ , see Figure 8-1, SEL = LOW or float      | 1.5  | 2                   |     | v     |

| V <sub>OD2</sub>                               | Driver differential output voltage                                      | $R_L=54\Omega$ , see Figure 8-1, SEL = HIGH                  | 2.1  | 3.6                 |     | v     |

| V <sub>OD3</sub>                               | Driver differential output voltage with<br>bus load                     | V <sub>test</sub> = -7V to 12V, see Figure 8-1               | 1.5  |                     |     | V     |

| $\Delta  V_{OD} $                              | Change in differential output voltage between two states                | $R_L$ =54 $\Omega$ , or $R_L$ =100 $\Omega$ , see Figure 8-1 | -0.2 |                     | 0.2 | V     |

| V <sub>OC</sub>                                | Common-mode output voltage                                              | $R_L=54\Omega$ , or $R_L=100\Omega$ , see Figure 8-1         | 1    | V <sub>ISO</sub> /2 | 3   | V     |

| $\Delta V_{OC}$                                | Change in steady-state common-mode<br>output voltage between two states | $R_L$ =54 $\Omega$ , or $R_L$ =100 $\Omega$ , see Figure 8-1 | -0.2 |                     | 0.2 | V     |

| I <sub>IH</sub> , I <sub>IL</sub>              | Input leakage current                                                   | DI, DE = low or high                                         | -20  |                     | 20  | μΑ    |

| $\int Chart circuit output current () = U(CU)$ |                                                                         | $DE = V_{CC}$ , $DI = 0V$ or $V_{CC}$ , $V_A$ or $V_B = -7V$ | 150  |                     | 150 |       |

| I <sub>os</sub> Short-circuit out              | Short-circuit output current (V <sub>0</sub> = HIGH)                    | $DE = V_{CC}$ , $DI = 0V$ or $V_{CC}$ , $V_A$ or $V_B = 12V$ | -150 |                     | 150 | mA    |

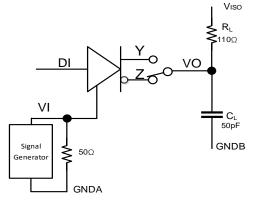

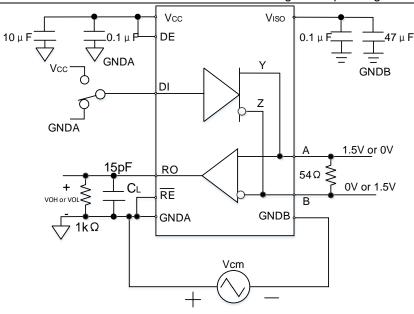

| CMTI                                           | Common mode transient immunity                                          | V <sub>CM</sub> = 1200V; See Figure 8-6                      | 100  | 150                 |     | kV/μS |

#### 7.7.2. Receiver

All typical specs are at  $V_{CC}$  = 5V,  $V_{CCL}$  =  $V_{CC}$ ,  $V_{ISOIN}$  =  $V_{ISO}$ ,  $T_A$  = 25°C, Min/Max specs are over recommended operating conditions unless otherwise specified.

|                      | Parameter                              | Test Condition                                            | Min                  | Тур. | Max | Unit   |  |

|----------------------|----------------------------------------|-----------------------------------------------------------|----------------------|------|-----|--------|--|

| V                    | Output logic high voltage              | V <sub>CC</sub> =5V, I <sub>OH</sub> =4mA                 | V <sub>CC</sub> -0.4 | 4.8  |     | v      |  |

| V <sub>OH</sub>      |                                        | V <sub>CC</sub> =3.3V, I <sub>OH</sub> =-4mA              | V <sub>CC</sub> -0.4 | 3    |     | v      |  |

| V                    | Output logic low voltage               | V <sub>CC</sub> =5V, I <sub>OL</sub> =4mA 0.2             |                      | 0.4  | V   |        |  |

| V <sub>OL</sub>      | Output logic low voltage               | V <sub>CC</sub> =3.3V, I <sub>OL</sub> =4mA               |                      | 0.2  | 0.4 | v      |  |

| V <sub>IT+(IN)</sub> | Positive-going input threshold voltage |                                                           |                      | -110 | -50 | mV     |  |

| V <sub>IT-(IN)</sub> | Negative-going input threshold voltage |                                                           | -200                 | -140 |     | mV     |  |

| V <sub>I(HYS)</sub>  | Receiver input hysteresis              |                                                           |                      | 30   |     | mV     |  |

|                      |                                        | $V_A$ or $V_B$ =12V, other inputs = 0 V                   |                      | 75   | 125 |        |  |

|                      | Pus input surrent                      | $V_A$ or $V_B$ =12V, $V_{CC}$ = 0 V, other inputs = 0 V   |                      | 80   | 125 | 125 μA |  |

| I <sub>I</sub>       | Bus input current                      | $V_A$ or $V_B = -7$ V, other inputs = 0 V                 | -100                 | -40  |     |        |  |

|                      |                                        | $V_A$ or $V_B = -7$ V, $V_{CC} = 0$ V, other inputs = 0 V | -100                 | -40  |     |        |  |

| IIH                  | Input current on RE pin                | V <sub>IH</sub> = V <sub>CC</sub>                         | -20                  |      | 20  | μΑ     |  |

| I <sub>IL</sub>      | Input current on RE pin                | V <sub>IL</sub> = 0 V                                     | -20                  |      | 20  | μΑ     |  |

| R <sub>ID</sub>      | Differential input resistance          | A, B, -7V < V <sub>CM</sub> < 12V                         | 96                   |      |     | ΚΩ     |  |

#### CA-IS2092W, CA-IS2092VW

Version 1.03, 2023/05/23

Shanghai Chipanalog Microelectronics Co., Ltd.

#### 7.8. Supply Current

All typical specs are at V<sub>CC</sub> = 5V, V<sub>CCL</sub> = V<sub>CC</sub>, V<sub>ISOIN</sub> = V<sub>ISO</sub>, T<sub>A</sub> = 25°C, Min/Max specs are over recommended operating conditions

|                        | Parameter                                       |                                            | Test Condition                  | on                               | Min  | Тур. | Max  | Uni    |  |

|------------------------|-------------------------------------------------|--------------------------------------------|---------------------------------|----------------------------------|------|------|------|--------|--|

| solated Pov            | wer Supply (without bus loa                     | d across A and B, un                       | less otherwise sp               | ecified.)                        |      |      |      |        |  |

|                        |                                                 | I <sub>ISO</sub> = 0 to 130mA,             | $V_{CC}$ = 5V, SEL = GN         | NDB or V <sub>ISO</sub>          | 4.75 | 5    | 5.25 |        |  |

| V <sub>ISO</sub>       | Isolated supply output                          | I <sub>ISO</sub> = 0 to 75mA, \            | / <sub>CC</sub> = 3.3V, SEL = G | NDB                              | 3.13 | 3.3  | 3.47 | V      |  |

|                        |                                                 |                                            | V <sub>CC</sub> = 5V            | , SEL = GNDB or V <sub>ISO</sub> |      | 130  |      |        |  |

|                        |                                                 | $R_L = NC^2$                               | V <sub>CC</sub> = 3.3           | 3V, SEL = GNDB                   |      | 75   |      |        |  |

|                        |                                                 |                                            | V <sub>CC</sub> = 5V            | , SEL = V <sub>ISO</sub>         |      | 80   |      |        |  |

|                        | Maximum load current <sup>1</sup>               | $R_L = 100\Omega$                          | V <sub>CC</sub> = 5V            | , SEL = GNDB                     |      | 105  |      |        |  |

| ISO                    | waximum load current*                           |                                            | V <sub>CC</sub> = 3.3           | 3V, SEL = GNDB                   |      | 40   |      | mA     |  |

|                        |                                                 |                                            | V <sub>CC</sub> = 5V            | , SEL = V <sub>ISO</sub>         |      | 55   |      |        |  |

|                        |                                                 | $R_L = 54\Omega$                           | V <sub>CC</sub> = 5V            | , SEL = GNDB                     |      | 85   |      |        |  |

|                        |                                                 |                                            | V <sub>CC</sub> = 3.3           | 3V, SEL = GNDB                   |      | 30   |      |        |  |

| .,                     |                                                 | $I_{ISO} = 50 \text{mA}, V_{CC} =$         | 4.5 to 5.5V, SEL =              | GNDB or VISO                     |      | 2    |      |        |  |

| V <sub>ISO(LINE)</sub> | DC line regulation                              | $I_{ISO} = 50 \text{mA}, V_{CC} =$         |                                 |                                  |      | 2    |      | mV/    |  |

| .,                     |                                                 | I <sub>ISO</sub> = 0 to 130mA,             |                                 |                                  |      | 4.07 |      |        |  |

| V <sub>ISO(LOAD)</sub> | DC load regulation                              | $I_{ISO} = 0$ to 75mA, \                   |                                 |                                  |      | 1%   |      |        |  |

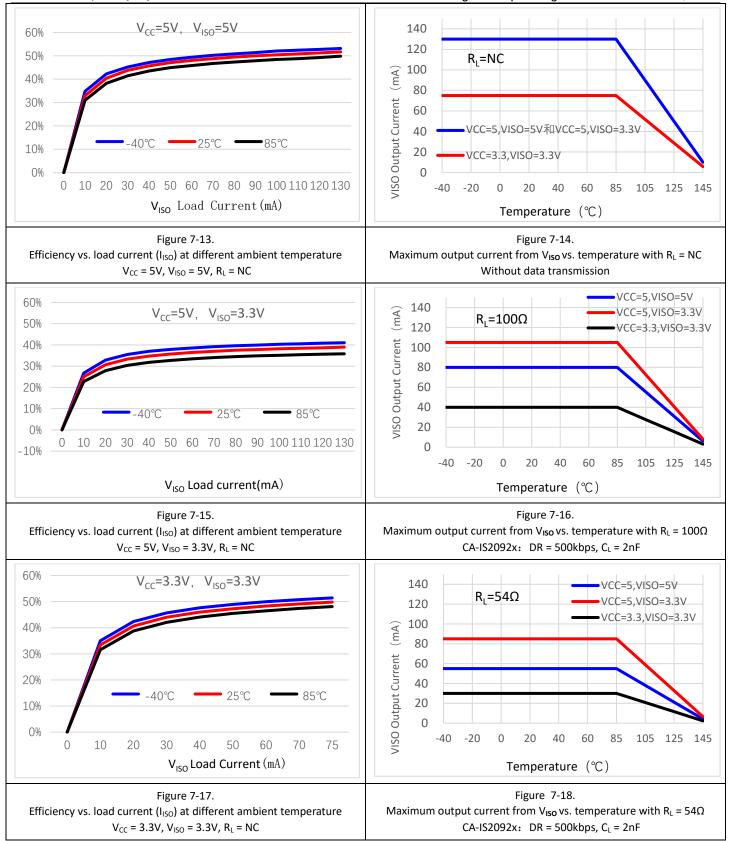

|                        |                                                 |                                            |                                 | $V_{CC}$ = 5V, SEL = $V_{ISO}$   |      | 53%  |      |        |  |

| EFF                    | Efficiency @ maximum                            | -                                          |                                 | $V_{CC}$ = 5V, SEL = GNDB        |      | 42%  |      |        |  |

|                        | load current                                    | I <sub>ISO</sub> = 75mA, C <sub>LOAD</sub> | = 0.1µF// 10µF                  | $V_{CC}$ = 3.3V, SEL = GNDB      |      | 47%  |      |        |  |

| Quiescent c            | urrent, DE = $V_{cc}$ , $\overline{RE}$ = 0V, D |                                            |                                 |                                  |      |      |      |        |  |

|                        |                                                 |                                            | V <sub>CC</sub> = 3.3\          | /, SEL = GNDB                    |      | 17   | 28   |        |  |

|                        |                                                 |                                            |                                 | /, SEL = GNDB                    |      | 15   | 22   | -      |  |

|                        |                                                 |                                            |                                 | /, SEL = V <sub>ISO</sub>        |      | 18   | 28   |        |  |

|                        |                                                 |                                            |                                 | /, SEL = GNDB                    |      | 94   | 125  |        |  |

|                        |                                                 | $R_L = 54\Omega$                           |                                 | /, SEL = GNDB                    |      | 82   | 120  |        |  |

|                        | Supply current on                               |                                            |                                 | /, SEL = V <sub>ISO</sub>        |      | 140  | 200  |        |  |

| lcc                    | logic side                                      |                                            |                                 | /, SEL = GNDB                    |      | 65   | 95   | mA     |  |

|                        | -                                               | R <sub>L</sub> = 100Ω                      |                                 | /, SEL = GNDB                    |      | 55   | 80   |        |  |

|                        |                                                 |                                            |                                 | /, SEL = V <sub>ISO</sub>        |      | 93   | 135  |        |  |

|                        |                                                 |                                            |                                 | /, SEL = GNDB                    |      | 57   | 88   |        |  |

|                        |                                                 | R <sub>L</sub> = 120Ω                      |                                 | /, SEL = GNDB                    |      | 50   | 72   |        |  |

|                        |                                                 |                                            |                                 | /, SEL = V <sub>ISO</sub>        |      | 83   | 120  |        |  |

| Average op             | erating current, DE = $V_{cc}$ , RE             | = 0V. DI = 250kHz so                       | uare-wave. 50%                  | duty cycle.                      |      |      |      |        |  |

|                        |                                                 |                                            |                                 | /, SEL = GNDB                    |      | 92   | 125  |        |  |

|                        |                                                 | R <sub>L</sub> = 54Ω                       |                                 | SEL = GNDB                       |      | 85   | 120  |        |  |

|                        |                                                 | 2 2                                        | $V_{CC} = 5V, S$                | -                                |      | 145  | 210  |        |  |

|                        |                                                 |                                            |                                 | /, SEL = GNDB                    |      | 65   | 95   |        |  |

| l <sub>cc</sub>        | Supply current on                               | R <sub>L</sub> = 100Ω                      |                                 | SEL = GNDB                       |      | 60   | 85   | mA     |  |

|                        | logic side                                      |                                            | $V_{cc} = 5V, S$                |                                  | 1    | 100  | 145  | - IIIA |  |

|                        |                                                 |                                            |                                 | /, SEL = GNDB                    | 1    | 60   | 85   |        |  |

|                        |                                                 | R <sub>L</sub> = 120Ω                      |                                 | SEL = GNDB                       | 1    | 55   | 80   |        |  |

|                        |                                                 |                                            |                                 | SEL = V <sub>ISO</sub>           |      | 95   | 140  |        |  |

找到引用源。, 错误!未找到引用源。, the maximum output current of V<sub>ISO</sub> vs. temperature. 2. R<sub>L</sub> is bus load across A and B, R<sub>L</sub>= NC means no-load connection between CANH and CANL.

#### 7.9. Switching Characteristics

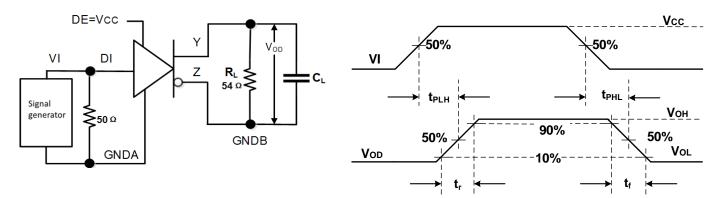

#### 7.9.1. Driver

All typical specs are at  $V_{CC} = 5V$ ,  $V_{CCL} = V_{CC}$ ,  $V_{ISOIN} = V_{ISO}$ ,  $T_A = 25$ °C, Min/Max specs are over recommended operating conditions unless otherwise specified.

|                                    | Parameters                                              | Test conditions | Minimum<br>value | ТҮР | Maximum<br>value | Unit |

|------------------------------------|---------------------------------------------------------|-----------------|------------------|-----|------------------|------|

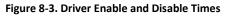

| t <sub>PLH</sub> ,t <sub>PHL</sub> | Driver Propagation Delay                                |                 |                  | 100 | 250              | ns   |

| t <sub>PWD</sub>                   | Driver output skew  t <sub>PLH</sub> - t <sub>PHL</sub> | See Figure 8-2  |                  | 5   | 20               | ns   |

| t <sub>r</sub> ,t <sub>f</sub>     | Differential output rise/full time                      |                 |                  | 150 | 500              | ns   |

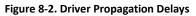

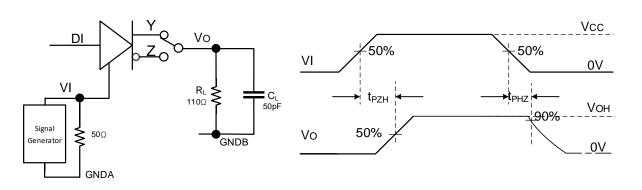

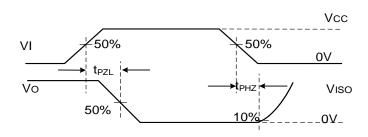

| t <sub>PZH</sub> ,t <sub>PZL</sub> | Driver enable time                                      |                 |                  | 300 | 800              | ns   |

| t <sub>PHZ</sub> ,t <sub>PLZ</sub> | Driver disable time                                     | See Figure 8-3  |                  | 20  | 50               | ns   |

#### 7.9.2. Receiver

All typical specs are at  $V_{CC}$  = 5V,  $V_{CCL}$  =  $V_{CC}$ ,  $V_{ISOIN}$  =  $V_{ISO}$ ,  $T_A$  = 25°C, Min/Max specs are over recommended operating conditions unless otherwise specified.

|                                    | Parameters                                                | Test conditions | Minimum<br>value | ТҮР | Maximum<br>value | Unit |

|------------------------------------|-----------------------------------------------------------|-----------------|------------------|-----|------------------|------|

| t <sub>PLH</sub> ,t <sub>PHL</sub> | Receiver propagation delay                                |                 |                  | 50  | 100              | ns   |

| t <sub>PWD</sub>                   | Receiver output skew  t <sub>PLH</sub> - t <sub>PHL</sub> | See Figure 8-4. |                  |     | 12               | ns   |

| t <sub>r</sub> ,t <sub>f</sub>     | Receiver output rise/full time                            |                 |                  | 2.5 | 4                | ns   |

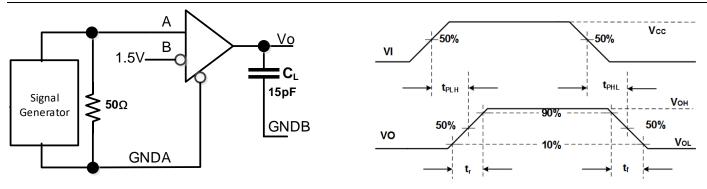

| t <sub>PHZ</sub> ,t <sub>PLZ</sub> | Receiver disable time                                     | Soo Eiguro 8 E  |                  | 20  | 50               | ns   |

| t <sub>PZH</sub> ,t <sub>PZL</sub> | Receiver enable time, DE = 0V                             | See Figure 8-5. |                  | 30  | 80               | ns   |

## CHIPANALOG

#### CA-IS2092W, CA-IS2092VW Version 1.03, 2023/05/23

Shanghai Chipanalog Microelectronics Co., Ltd.

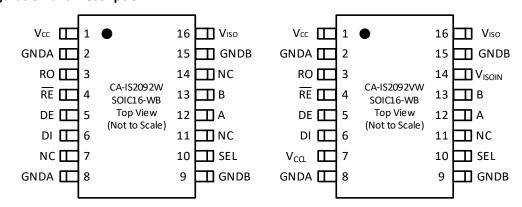

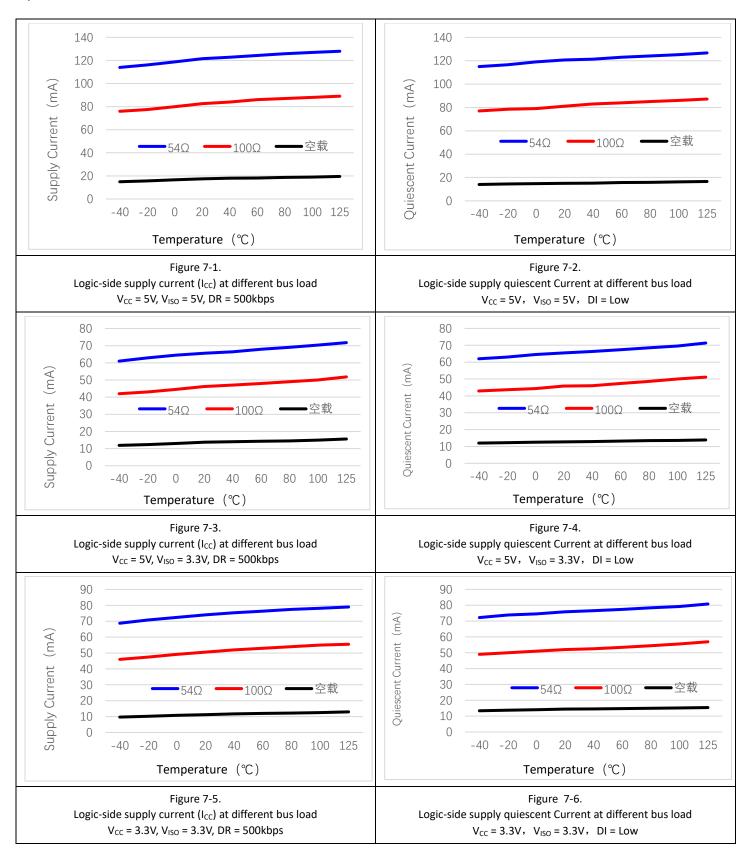

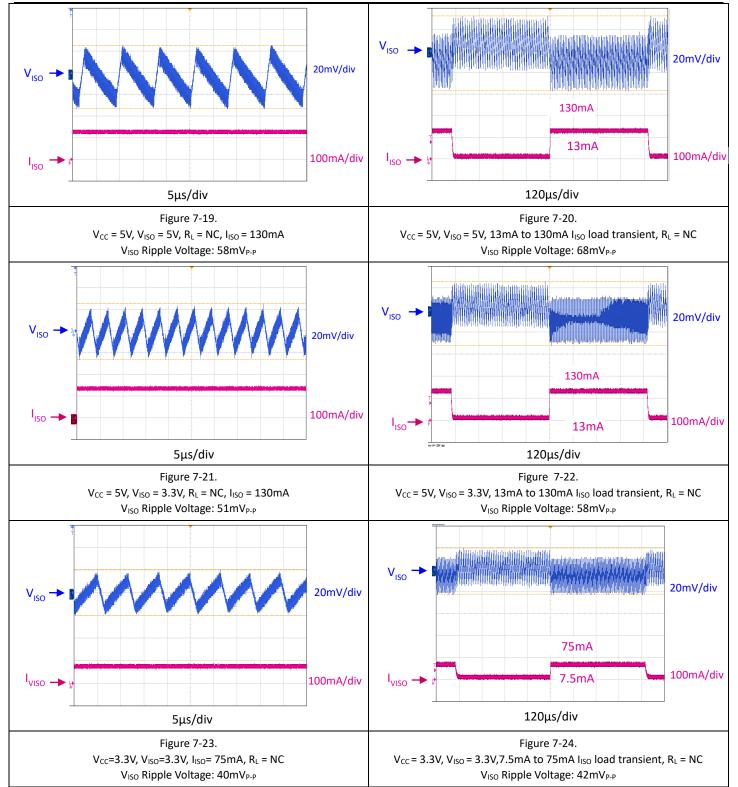

#### 7.10. Typical Operating Characteristics

All typical specs are at  $V_{CC} = 5V$ ,  $V_{CCL} = V_{CC}$ ,  $V_{ISOIN} = V_{ISO}$ ,  $T_A = 25^{\circ}C$ , Min/Max specs are over recommended operating conditions unless otherwise specified.

#### CA-IS2092W, CA-IS2092VW Version 1.03, 2023/05/23

## CA-IS2092W, CA-IS2092VW

Version 1.03, 2023/05/23

Shanghai Chipanalog Microelectronics Co., Ltd.

#### CA-IS2092W, CA-IS2092VW Version 1.03, 2023/05/23

#### CA-IS2092W, CA-IS2092VW Version 1.03, 2023/05/23

8. Parameter Measurement Information

Figure 8-4. Receiver Propagation Delays

Figure 8-5. Receiver Enable and Disable Times

#### Notes:

- 1.  $R_L = 110 \Omega$  for RS422,  $R_L = 54 \Omega$  for RS-485

- 2.  $C_L$  includes external circuit (fixture and instrumentation etc.) capacitance.

Figure 8-6. Common Mode Transient Immunity (CMTI) Test for the Half-duplex

#### 9. Detailed Description

The CA-IS2092 isolated half-duplex RS-485/RS-422 transceivers provide up to 2.5kV<sub>RMS</sub> of galvanic isolation between the cable side (bus-side) of the transceiver and the controller side (logic-side). These devices feature up to 150kV/µs common mode transient immunity, allow up to 0.5Mbps communication across an isolation barrier. Power isolation is achieved with an integrated DC-DC convertor to generate a regulated 3.3V or 5V supply for the cable-side circuit. These devices do not require any external components other than bypass capacitors and bus termination resistors to realize an isolated RS-485/RS-422 port. Robust isolation coupled with extended ESD protection and increased speed enables efficient communication in noisy environments, making them ideal for long distance transmission and multi-drop communication in a wide range of applications such as motor drives, PLC communication modules, telecom rectifiers, elevators, HVACs etc. systems. Two mechanisms against excessive power dissipation caused by faults or bus contention. The first, over-current protection on the output stage, provides immediate protection against short circuits over the entire common-mode voltage range. The second, a thermal shutdown circuit, forces the driver outputs into a high-impedance state.

#### 9.1. Logic Input

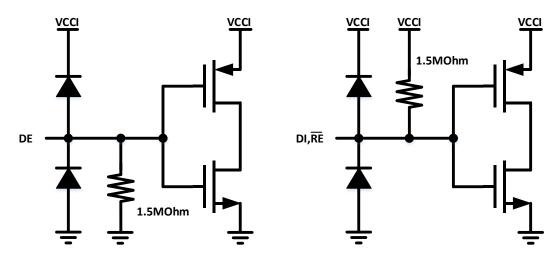

The CA-IS2092x devices include three logic inputs on the logic side: receiver enable, driver enable and driver digital input. The driver enable control DE pin has an internal weak pull-down to GNDA, while the digital input DI and receiver enable pins have an internal pull-up to  $V_{cc}/V_{ccL}$ , see Figure 9-1 the input equivalent circuit.

Figure 9-1. Input equivalent circuit

#### 9.2. Fail-Safe Receiver

The receiver reads the differential input from the bus line (A and B) and transfers this data as a single-ended, logic-level output RO to the controller. Driving the enable input  $\overline{\text{RE}}$  low to enable the receiver. Driving  $\overline{\text{RE}}$  logic high to disable the receiver. RO is high impedance when  $\overline{\text{RE}}$  is logic high. The  $\overline{\text{RE}}$  pin has an internal pull-up resistor to V<sub>CC</sub> for CA-IS2092W or V<sub>CCL</sub> for CA-IS2092VW.

The CA-IS2092x family of RS-485/RS-422 transceivers do not require external fail-safe bias resistors because a true failsafe feature is integrated into the devices. In true fail-safe, the receiver's positive-going input threshold is  $V_{IT+(IN)}$  (-110mV, typ. and -50mV, max.), if the differential receiver input voltage of  $V_A-V_B$  is greater than or equal to  $V_{IT+(IN)}$ , RO is logic high when  $\overline{RE}$ is low; RO is logic low when  $V_A-V_B$  is less than or equal to  $V_{IT-(IN)}$  in case the receiver is enabled; thereby eliminating the need for fail-safe bias resistors while complying fully with the RS-485 standard, see Table 9-1 the receiver truth table. Fail-safe feature is used to keep the receiver's output in a defined state when the receiver is not connected to the cable, the cable has an open or the cable has a short.

Table 9-1. Receiver Truth Table

| <b>DIFFERENTIAL INPUT:</b> $V_{ID} = (V_A - V_B)$                                         | ENABLE (RE) | OUTPUT (RO)   |  |  |  |  |

|-------------------------------------------------------------------------------------------|-------------|---------------|--|--|--|--|

| $V_{IT+(IN)} \leq V_{ID}$                                                                 | L           | Н             |  |  |  |  |

| $V_{IT-(IN)} < V_{ID} < V_{IT+(IN)}$                                                      | L           | Indeterminate |  |  |  |  |

| $V_{ID} \leq V_{IT-(IN)}$                                                                 | L           | L             |  |  |  |  |

| X                                                                                         | Н           | Hi-Z          |  |  |  |  |

| Open/Short/Idle                                                                           | L           | Н             |  |  |  |  |

| X Open Hi-Z                                                                               |             |               |  |  |  |  |

| Notes:                                                                                    |             |               |  |  |  |  |

| <ol> <li>X = don't care; H = high level; L = low level; Hi-Z = high impedance.</li> </ol> |             |               |  |  |  |  |

| 2. $\overline{\text{RE}}$ has an internal weak pull-up to V <sub>CC</sub> .               |             |               |  |  |  |  |

#### 9.3. Driver

The transmitter converts a single-ended input signal (DI) from the local controller to differential outputs on the bus lines A and B. The truth table for the transmitter is provided in Table 9-2, the driver enable control DE pin has an internal weak pull-down to GNDA, see Figure 9-1 the input equivalent circuit; while the digital input DI pin has an internal pull-up to  $V_{CC}$  for CA-IS2092W or  $V_{CCL}$  for CA-IS2092VW. The driver outputs and receiver inputs on the bus side are protected from ±20kV electrostatic discharge (ESD) to GNDB, as specified by the Human Body Model (HBM). The driver outputs also feature short-circuit protection and thermal shutdown.

#### Table 9-2. Transmitter Truth Table

| T <sub>x</sub> INPUT                                                                      | ENABLE INPUT | OUTPUT |      |  |  |  |

|-------------------------------------------------------------------------------------------|--------------|--------|------|--|--|--|

| (DI)                                                                                      | (DE)         | А      | В    |  |  |  |

| н                                                                                         | Н            | Н      | L    |  |  |  |

| L                                                                                         | Н            | L      | Н    |  |  |  |

| Х                                                                                         | L            | Hi-Z   | Hi-Z |  |  |  |

| Х                                                                                         | OPEN         | Hi-Z   | Hi-Z |  |  |  |

| OPEN H H L                                                                                |              |        |      |  |  |  |

| Notes:                                                                                    |              |        |      |  |  |  |

| <ol> <li>X = don't care; H = high level; L = low level; Hi-Z = high impedance.</li> </ol> |              |        |      |  |  |  |

2. DE pin has an internal weak pull-down to GNDA, and DI pin has an internal pull-up to  $V_{CC}/V_{CCL}$ .

#### 9.4. Protection Functions

#### 9.4.1. Signal Isolation and Power Isolation

The CA-IS2092x devices integrated digital galvanic isolators using Chipanalog's capacitive isolation technology based on the ON-OFF keying (OOK) modulation scheme, allow data transmission between the controller side and cable side of the transceiver with different power domains. Also, the power isolation is achieved with an integrated DC-DC convertor to generate a regulated 3.3V or 5V supply for the cable-side.

#### 9.4.2. Undervoltage Lockout

Both CA-IS2092V and CA-IS2092VW have undervoltage detection on  $V_{CC}$  supply terminal, the CA-IS2092VW also features undervoltage detection on  $V_{CCL}$  supply terminal, that place the device in protected mode during an undervoltage event on  $V_{CCL}$ or/and  $V_{CC}$ , see Table 9-3 and Table 9-4. Once the undervoltage condition is cleared and the supply voltage has returned to a valid level, the devices transition to normal mode. The host controller should not attempt to send or receive messages until the device enters normal operation.

#### Table 9-3. CA-IS2092W Undervoltage Lockout

| V <sub>cc</sub>          | DEVICE STATE   | BUS OUTPUT     | RXD            |

|--------------------------|----------------|----------------|----------------|

| > V <sub>CC(UVLO+)</sub> | Normal         | Per TXD        | Mirrors Bus    |

| < V <sub>CC(UVLO_)</sub> | Protected mode | High Impedance | High Impedance |

#### Table 9-4. CA-IS2092VW Undervoltage Lockout

| V <sub>cc</sub>          | V <sub>CCL</sub>           | DEVICE STATE   | BUS OUTPUT     | RXD            |

|--------------------------|----------------------------|----------------|----------------|----------------|

| > V <sub>CC(UVLO+)</sub> | > V <sub>CCL(UVLO+)</sub>  | Normal         | Per TXD        | Mirrors Bus    |

| < V <sub>CC(UVLO_)</sub> | > V <sub>CCL(UVLO+)</sub>  | Protected mode | High Impedance | High Impedance |

| > V <sub>CC(UVLO+)</sub> | < V <sub>CCL(UVLO_</sub> ) | Protected mode | High Impedance | High Impedance |

| < V <sub>CC(UVLO_)</sub> | < V <sub>CCL(UVLO_</sub> ) | Protected mode | High Impedance | High Impedance |

#### 9.4.3. Thermal Shutdown

If the junction temperature of the CA-IS2092x device exceeds the thermal shutdown threshold  $T_{J(shutdown)}$  (180°C, typ.), the driver outputs go high-impedance state. The shutdown condition is cleared when the junction temperature drops to normal operation temperature range of the device(160°C, typ.).

#### 9.4.4. Current-Limit

The CA-IS2092x protect the transmitter output stage against a short-circuit to a positive or negative voltage over the common mode voltage range of -7V to 12V by limiting the driver current. However, this will cause large supply current and dissipation. Thermal shutdown further protects the devices from excessive temperatures that may result from a short circuit fault. The transmitter returns to normal operation once the short is removed.

#### 9.5. Isolated Supply Output

The integrated DC-DC converter provide up to 650mW of isolated power with +3.3V or +5V fixed output voltage configurations. , depending on the SEL pin status, see Table 9-5 for the supply configurations of CA-IS2092x devices. Get the SEL pin fixed (connect to  $V_{ISO}$  or GNDB) before power on the transceivers.

| Table 9-5. Supply Configuration |

|---------------------------------|

|---------------------------------|

| SEL INPUT                   | V <sub>cc</sub>    | V <sub>ISO</sub>  |

|-----------------------------|--------------------|-------------------|

| Shorted to V <sub>ISO</sub> | 5 V                | 5V                |

| Shorted to GNDB or floating | 5 V                | 3.3V              |

| Shorted to GNDB or floating | 3.3 V <sup>1</sup> | 3.3V <sup>2</sup> |

Notes:

1.  $V_{DD}$  = 3.3 V, SEL shorted to  $V_{ISO}$  (essentially  $V_{ISO}$  = 5 V) is not recommended.

2. The SEL pin has a weak pull-down internally. However, for  $V_{ISO}$  = 3.3 V, the SEL pin should be connected to the GNDB externally, especially in the noisy system.

The maximum output current from V<sub>ISO</sub> is shown as Table 9-6. Note that the I<sub>ISO</sub> value in Table 9-6 is the maximum output current at +25°C with data rate x load capacitance < 0.5Mbps × 2nF. As the increase of temperature, especially when the temperature exceeds +85°C, the maximum load current will be decreased, see more details in 错误!未找到引用源。, 错误!未找到引用源。.

#### CA-IS2092W, CA-IS2092VW Version 1.03, 2023/05/23

Shanghai Chipanalog Microelectronics Co., Ltd.

Table 9-6. Maximum Output Current of V<sub>ISO</sub> @ T<sub>A</sub> = 25°C

| Supply voltage V <sub>CC</sub> (V) | V <sub>ISO</sub> (V) | $R_L(\Omega)$ between CANH and CANL | l <sub>iso</sub> (mA) |  |

|------------------------------------|----------------------|-------------------------------------|-----------------------|--|

| 4.5~5.5                            | 5                    |                                     | 130                   |  |

| 4.5~5.5                            | 3.3                  | NC <sup>1</sup>                     | 130                   |  |

| 3.15~3.6                           | 3.3                  |                                     | 75                    |  |

| 4.5~5.5                            | 5                    |                                     | 80                    |  |

| 4.5~5.5                            | 3.3                  | 100                                 | 105                   |  |

| 3.15~3.6                           | 3.3                  |                                     | 40                    |  |

| 4.5~5.5                            | 5                    |                                     | 55                    |  |

| 4.5~5.5                            | 3.3                  | 54                                  | 85                    |  |

| 3.15~3.6                           | 3.3                  |                                     | 30                    |  |

| :                                  |                      | •                                   |                       |  |

#### **10.** Applications Information

#### 10.1. Overview

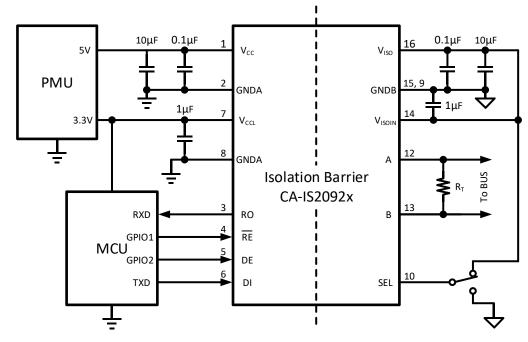

The CA-IS2092 family of half-duplex RS-485/RS-422 transceivers commonly used for asynchronous data transmissions. For half-duplex devices, the driver and receiver enable pins allow for the configuration of different operating modes. Because of high peak currents flowing through  $V_{CC}$  and  $V_{ISO}$  supplies, bulk capacitance of typical 10µF (or at least 4.7µF) is recommended on both pins. Higher values of bulk capacitors are helpful to reduce noise and ripple further and enhance performance, see Figure 10-1 the typical application circuit. Make sure there is no data transmission during the CA-IS2092X power up.

Figure 10-1. Typical application circuit

#### 10.2. Typical Application

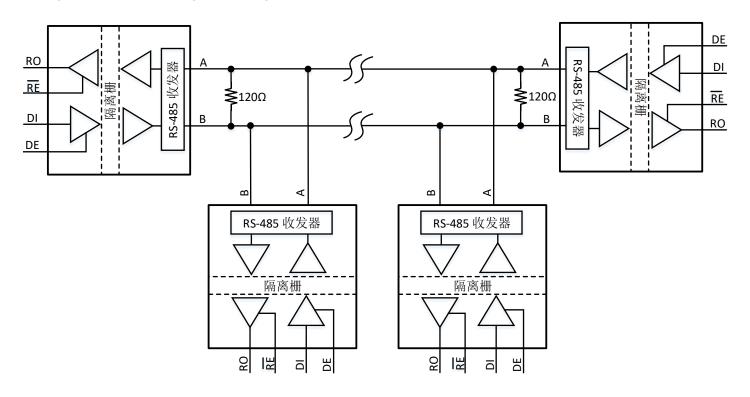

An RS-485 bus consists of multiple transceivers connecting in parallel to a bus cable. As seen in the following typical network application circuit, Figure 10-2. The maximum recommended data rate in the RS-485/RS422 network is 10Mbps, which can be achieved at a maximum cable length of 40ft (12m). The absolute maximum distance is 4000ft (1.2km) of cable, at which point, data rate is limited to 100kbps. These were the specifications made in the original RS-485 standard, new RS-485/RS-422 transceivers and cables are pushing the limit of RS-485 far beyond its original definitions. However, the maximum data rate is still limited by the bus loading, number of nodes, cable length etc. factors. For RS-485 network design, margin must be given for signal loss across the system and cabling, parasitic loadings, timing, network imbalances, ground offsets and signal integrity thus a practical maximum data rate, number of nodes often lower. To minimize reflections, terminate the line at both ends with a termination resistor (120 $\Omega$  in the typical application circuits), whose value matches the characteristic impedance(Z<sub>0</sub>) of the cable, and keep stub lengths off the main line as short as possible. As a general rule moreover, termination resistors should be placed at both far ends of the cable. This method, known as parallel termination, generally allows for higher data rates over longer cable length.

Figure 10-2. Typical isolated half-duple RS-485 application circuit

#### 10.3. 256 transceivers on the bus

The maximum number of transceivers and receivers allowed depends on how much each device loads down the system. All devices connected to an RS-485 network should be characterized in regard to multiples or fractions of unit loads. The maximum number of unit loads allowed one twisted pair, assuming a properly terminated cable with a characteristic impedance of 120 $\Omega$  or more, is 32 (375 $\Omega$ ). The CA-IS2092x transceivers have a 1/8-unit load (96k $\Omega$ ) receiver, which allows up to 256 transceivers, connected in parallel, on one communication line.

# CHIPANALOG

## CA-IS2092W, CA-IS2092VW

Version 1.03, 2023/05/23

Shanghai Chipanalog Microelectronics Co., Ltd.

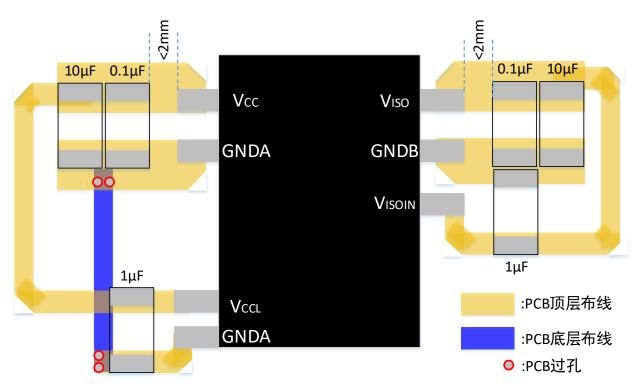

#### 10.4. PCB Layout

Careful PCB layout is critical to achieve clean and stable communication operation. It is recommended to design an isolation channel underneath the isolator that is free from ground and signal planes. Any galvanic or metallic connection between the cable side and logic side will defeat the isolation. To make sure device operation is reliable at all data rates and supply voltages, the minimum  $0.1\mu F//10\mu$ F decoupling capacitors between V<sub>CC</sub> and GNDA, between V<sub>ISO</sub> and GNDB are recommended. For the individual logic supply input V<sub>CCL</sub> and V<sub>ISOIN</sub>, we recommend to use a 1µF ceramic capacitors with X5R or X7R between V<sub>CCL</sub> pin and GNDA, V<sub>ISOIN</sub> and GNDB. Place the bypass capacitors, and the CA-IS2092x IC on the same PCB layer. Place decoupling capacitors as close as possible to the CA-IS2092x device pins, see Figure 10-3 recommended components placement for the PCB layout. The paths must be wide and short to minimize inductance, also any via holes must be avoided on these paths.

Figure 10-3. Recommended PCB Layout

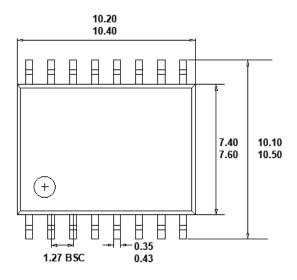

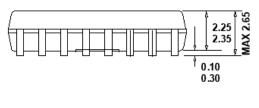

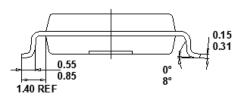

#### 11. Package Information

16-Pin Wide Body SOIC Package Outline

TOP VIEW

FRONT VIEW

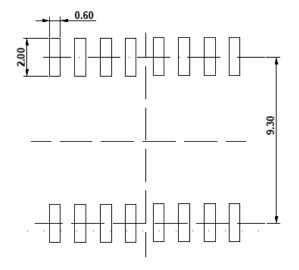

#### **RECOMMMENDED LAND PATTERN**

LEFT SIDE VIEW

#### Note:

1. All dimensions are in millimeters, angles are in degrees.

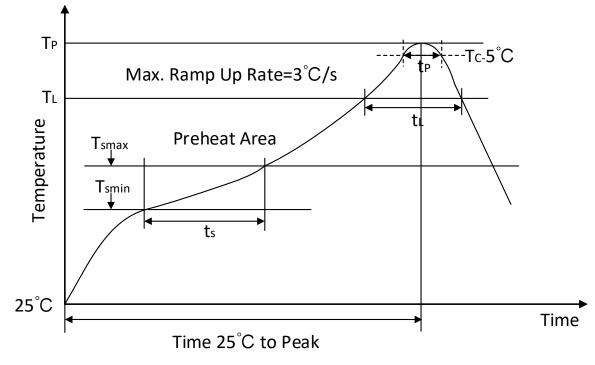

12. Soldering Temperature (reflow) Profile

| Profile Feature                                                                  | Pb-Free Assembly            |  |  |  |  |  |  |  |

|----------------------------------------------------------------------------------|-----------------------------|--|--|--|--|--|--|--|

| Average ramp-up rate(217 $^\circ\!\! C$ to Peak)                                 | 3℃ /second max              |  |  |  |  |  |  |  |

| Time of Preheat temp(from 150 $^\circ\!\mathrm{C}$ to 200 $^\circ\!\mathrm{C}$ ) | 60-120 second               |  |  |  |  |  |  |  |

| Time to be maintained above 217 $^\circ \!\!\! \mathbb{C}$                       | 60-150 second               |  |  |  |  |  |  |  |

| Peak temperature                                                                 | 260 +5/-0 ℃                 |  |  |  |  |  |  |  |

| Time within 5 $^\circ C$ of actual peak temp                                     | 30 second                   |  |  |  |  |  |  |  |

| Ramp-down rate                                                                   | 6 $^{\circ}$ C /second max. |  |  |  |  |  |  |  |

| Time from 25 $^\circ C$ to peak temp                                             | 8 minutes max               |  |  |  |  |  |  |  |

Table. 12-1 Soldering Temperature Parameter

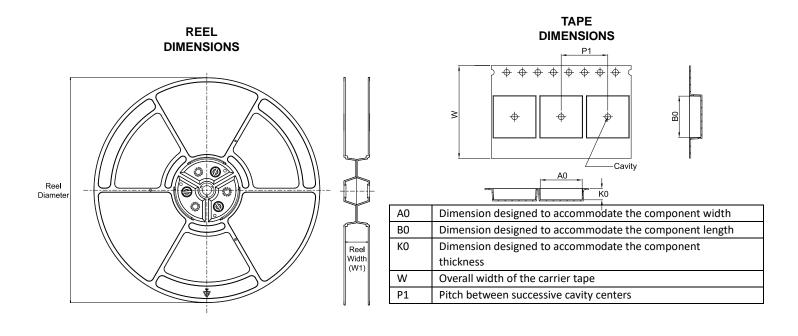

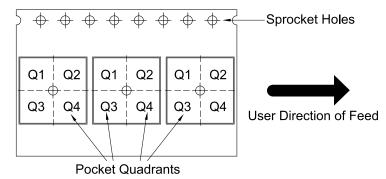

#### 13. Tape And Reel Information

#### **QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE**

\*All dimensions are nominal

| Device      | Package<br>Type | Package<br>Drawing | Pins | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-------------|-----------------|--------------------|------|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| CA-IS2092W  | SOIC            | W                  | 16   | 1000 | 330                      | 16.4                     | 10.9       | 10.7       | 3.2        | 12.0       | 16.0      | Q1               |

| CA-IS2092VW | SOIC            | W                  | 16   | 1000 | 330                      | 16.4                     | 10.9       | 10.7       | 3.2        | 12.0       | 16.0      | Q1               |

#### CA-IS2092W, CA-IS2092VW Version 1.03, 2023/05/23

Shanghai Chipanalog Microelectronics Co., Ltd.

#### 14. Important Statement

The above information is for reference only and intended to help Chipanalog customers with design, research and development. Chipanalog reserves the rights to change the above information due to technological innovation without advance notice.

All Chipanalog products pass ex-factory test. As for specific practical applications, customers need to be responsible for evaluating and determining whether the products are applicable or not by themselves. Chipanalog's authorization for customers to use the resources are only limited to development of the related applications of the Chipanalog products. In addition to this, the resources cannot be copied or shown, and Chipanalog is not responsible for any claims, compensations, costs, losses, liabilities and the like arising from the use of the resources.

#### **Trademark information**

Chipanalog Inc.<sup>®</sup> and Chipanalog<sup>®</sup> are registered trademarks of Chipanalog.

http://www.chipanalog.com